| 佐藤 真平 東京工業大学 学術国際情報センター 産学官連携研究員 |

[背景]LSIに集積されるトランジスタ数が増加し,メニーコアの時代に

[問題]メニーコアプロセッサの効率のよい設計

[貢献]効率の良いメニーコアプロセッサ設計環境の実現

[問題]メニーコアプロセッサの効率のよい設計

[貢献]効率の良いメニーコアプロセッサ設計環境の実現

プロセッサなどのLSIに集積されるトランジスタ数は増加している.それに伴い,プロセッサの性能向上は,これまでのシングルコアのプロセッサによる性能向上から,複数のコアを搭載するマルチコアプロセッサ,メニーコアによる性能向上へとシフトしている.

プロセッサなどのLSIの設計はアーキテクチャ設計,論理設計,回路設計,物理設計というフローで行われる.主に,アーキテクチャ設計と論理設計においてアーキテクチャの評価が必要となる.一般に,アーキテクチャ設計と論理設計では,同じハードウェアのために異なる言語による記述がなされており,複雑なハードウェアになるほどそれぞれの記述の等価性を検証するコストが高くなる.メニーコア時代の効率的なアーキテクチャの設計,評価には,この検証のコストを改善する必要がある.

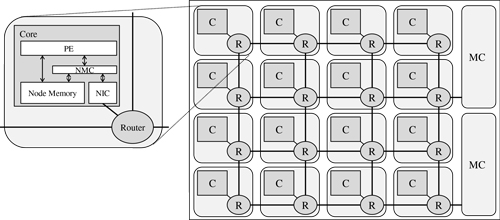

一方,マルチコアプロセッサ,メニーコアプロセッサでは並列処理によりアプリケーションの性能向上を図る.複数のコアを用いた並列処理にはコア間の通信が不可欠であり,メニーコアプロセッサでは,従来のバスによる通信では性能不足なため,Network-on-Chip(NoC)と呼ばれるルータを介したネットワークが用いられる.メニーコアプロセッサの設計において,NoCのルータアーキテクチャが重要な要素となる.

本研究では,アーキテクチャを効率的に設計,評価することができる新しいハードウェア記述言語ArchHDLを提案する.そして,メニーコアプロセッサに必要不可欠な要素であるNoCルータを提案し,それを搭載するメニーコアプロセッサを設計する.設計するハードウェアの評価には提案する新しいハードウェア記述言語を用いる.

ArchHDLはハードウェアをVerilog HDLなどのハードウェア記述言語と同じ抽象度でC++を用いて記述する.また,ArchHDLのソースコードをVerilog HDLに自動変換するツールも提供している.これによりC++による高速なシミュレーションを達成しつつ,Verilog HDLに変換できるため,効率的にアーキテクチャ設計,論理設計を行うことができる.

次に,メニーコアプロセッサを設計するにあたり,重要な要素である高性能なNoCルータアーキテクチャを提案する.高スループットなNoCルータとしてDistributed Shared-Buffer Router(DSB ルータ)が知られている.しかし,このルータはルータ内でのパケットの特殊なバッファリングによりレイテンシの点で典型的なNoCルータに劣る.そこで,ルータが低負荷時にパケットのバッファリングにかかわるレイテンシを削減する手法を提案する.これより,DSBルータの特徴であるスループットの性能を維持しつつ低レイテンシ化を達成する.

プロセッサなどのLSIの設計はアーキテクチャ設計,論理設計,回路設計,物理設計というフローで行われる.主に,アーキテクチャ設計と論理設計においてアーキテクチャの評価が必要となる.一般に,アーキテクチャ設計と論理設計では,同じハードウェアのために異なる言語による記述がなされており,複雑なハードウェアになるほどそれぞれの記述の等価性を検証するコストが高くなる.メニーコア時代の効率的なアーキテクチャの設計,評価には,この検証のコストを改善する必要がある.

一方,マルチコアプロセッサ,メニーコアプロセッサでは並列処理によりアプリケーションの性能向上を図る.複数のコアを用いた並列処理にはコア間の通信が不可欠であり,メニーコアプロセッサでは,従来のバスによる通信では性能不足なため,Network-on-Chip(NoC)と呼ばれるルータを介したネットワークが用いられる.メニーコアプロセッサの設計において,NoCのルータアーキテクチャが重要な要素となる.

本研究では,アーキテクチャを効率的に設計,評価することができる新しいハードウェア記述言語ArchHDLを提案する.そして,メニーコアプロセッサに必要不可欠な要素であるNoCルータを提案し,それを搭載するメニーコアプロセッサを設計する.設計するハードウェアの評価には提案する新しいハードウェア記述言語を用いる.

ArchHDLはハードウェアをVerilog HDLなどのハードウェア記述言語と同じ抽象度でC++を用いて記述する.また,ArchHDLのソースコードをVerilog HDLに自動変換するツールも提供している.これによりC++による高速なシミュレーションを達成しつつ,Verilog HDLに変換できるため,効率的にアーキテクチャ設計,論理設計を行うことができる.

次に,メニーコアプロセッサを設計するにあたり,重要な要素である高性能なNoCルータアーキテクチャを提案する.高スループットなNoCルータとしてDistributed Shared-Buffer Router(DSB ルータ)が知られている.しかし,このルータはルータ内でのパケットの特殊なバッファリングによりレイテンシの点で典型的なNoCルータに劣る.そこで,ルータが低負荷時にパケットのバッファリングにかかわるレイテンシを削減する手法を提案する.これより,DSBルータの特徴であるスループットの性能を維持しつつ低レイテンシ化を達成する.

最後に,メニーコアプロセッサを設計し評価する.研究・教育を目的として設計されたメニーコアアーキテクチャM-Coreをベースに,提案する高性能なNoCルータを搭載し,ハードウェアに改良を加えたメニーコアプロセッサを設計する(図).並列アプリケーションを用いたプロセッサ全体の評価により高性能なNoCルータによる性能向上を示す.

(2015年6月10日受付)