(邦訳:超低電力大規模集積回路のための電力効率の高い基板バイアス制御)

| 奥原 颯 University of Bologna, Research Fellow |

キーワード

| 集積回路 | 低電力設計 | 適応的電圧制御 |

[背景]IoTやウェアラブルデバイス等の低電力集積回路の需要の増加

[問題]低電力システムにおける基板バイアス制御のオーバヘッド

[貢献]ボディバイアス制御の高効率化と新たな制御手法の提案

技術の発展に伴い,さまざまなものが集積回路を内蔵するようになった.たとえば,個人用のPCのみならず,ウェアラブルデバイスやIoTノード等,組み込み用途にも幅広く用いられている.組み込み用途のシステムでは利用できる電力は必ずしも潤沢ではなく,これに内蔵される集積回路はより高効率かつ低電力で実装される必要がある.

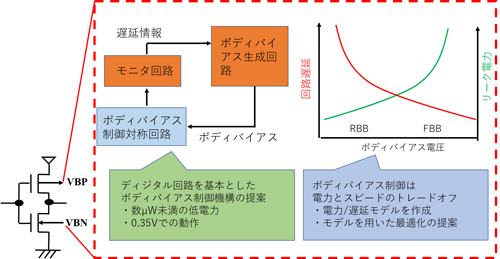

このような需要に伴い,Fully-Depleted Silicon on Insulator(FD-SOI)と呼ばれるトランジスタが開発された.一般に,集積回路の電力は電源電圧/ボディバイアス(図内VBP VBN)を制御することで調節できることが知られているが,最新のFD-SOIはこの点において良好な特性を持つ.特にボディバイアス制御の効果が従来のトランジスタよりもきわめて高く,これを活用することが望まれている.そこで本研究では従来のボディバイアス制御手法よりさらに効率的かつ低電力オーバヘッドを達成できる方法を提案した.

ボディバイアスを制御するにあたり問題になるのは,遅延と電力にトレードオフを持つことである.すなわち,対象とするシステム・要求性能に対する最適な電圧条件を求める必要がある.よって,初めに本研究では実チップを用いて電力・遅延モデルの係数を取得し,そのモデルを元に最適化を行う手法を提案した.このモデルを構築することで実際の測定の手間を削減し,簡単に最適化ができる.提案手法ではnMOSとpMOSのボディバイアスバランスが非対称な点も考慮されており,従来手法に比べて制御効率が高い.実験の結果,ボディバイスバランスが対称である最適化と比較して最大で20%以上の電力を削減することができた.さらに,チップとモデルとの誤差を調節する軽量なオンチップシステムアーキテクチャも提案している.

次に,ボディバイアスの電圧をどう制御するかも重要な課題である.低電力システムへの応用を目指す際には,この制御機構そのもので消費する電力も最小化しなければならない.そこで,本研究では,ディジタル回路を基本としたボディバイアス制御回路(Digitally assisted Automatic Body-bias Tuning (DABT) Scheme)を提案し,実チップ実装および実機検証を行った.本手法では対象とするシステムの遅延をモニタし,ボディバイアス電圧を要求される動作周波数が達成できるように制御する.アナログ回路と比較して,ディジタル回路は低い電源電圧での動作が容易で,この特性を用いた提案手法は最小で0.35Vでの動作に成功している.このときの電力オーバヘッドは数µW未満であった.

本研究成果を用いることで,より効率的なボディバイアス制御が可能になるだけでなく,制御に必要とする電力リソースの制限が緩和され,より幅広くボディバイアスが利用されることが期待される.

[貢献]ボディバイアス制御の高効率化と新たな制御手法の提案

技術の発展に伴い,さまざまなものが集積回路を内蔵するようになった.たとえば,個人用のPCのみならず,ウェアラブルデバイスやIoTノード等,組み込み用途にも幅広く用いられている.組み込み用途のシステムでは利用できる電力は必ずしも潤沢ではなく,これに内蔵される集積回路はより高効率かつ低電力で実装される必要がある.

このような需要に伴い,Fully-Depleted Silicon on Insulator(FD-SOI)と呼ばれるトランジスタが開発された.一般に,集積回路の電力は電源電圧/ボディバイアス(図内VBP VBN)を制御することで調節できることが知られているが,最新のFD-SOIはこの点において良好な特性を持つ.特にボディバイアス制御の効果が従来のトランジスタよりもきわめて高く,これを活用することが望まれている.そこで本研究では従来のボディバイアス制御手法よりさらに効率的かつ低電力オーバヘッドを達成できる方法を提案した.

ボディバイアスを制御するにあたり問題になるのは,遅延と電力にトレードオフを持つことである.すなわち,対象とするシステム・要求性能に対する最適な電圧条件を求める必要がある.よって,初めに本研究では実チップを用いて電力・遅延モデルの係数を取得し,そのモデルを元に最適化を行う手法を提案した.このモデルを構築することで実際の測定の手間を削減し,簡単に最適化ができる.提案手法ではnMOSとpMOSのボディバイアスバランスが非対称な点も考慮されており,従来手法に比べて制御効率が高い.実験の結果,ボディバイスバランスが対称である最適化と比較して最大で20%以上の電力を削減することができた.さらに,チップとモデルとの誤差を調節する軽量なオンチップシステムアーキテクチャも提案している.

次に,ボディバイアスの電圧をどう制御するかも重要な課題である.低電力システムへの応用を目指す際には,この制御機構そのもので消費する電力も最小化しなければならない.そこで,本研究では,ディジタル回路を基本としたボディバイアス制御回路(Digitally assisted Automatic Body-bias Tuning (DABT) Scheme)を提案し,実チップ実装および実機検証を行った.本手法では対象とするシステムの遅延をモニタし,ボディバイアス電圧を要求される動作周波数が達成できるように制御する.アナログ回路と比較して,ディジタル回路は低い電源電圧での動作が容易で,この特性を用いた提案手法は最小で0.35Vでの動作に成功している.このときの電力オーバヘッドは数µW未満であった.

本研究成果を用いることで,より効率的なボディバイアス制御が可能になるだけでなく,制御に必要とする電力リソースの制限が緩和され,より幅広くボディバイアスが利用されることが期待される.

(2019年5月31日受付)