| 神保 潮 東芝メモリ(株) |

キーワード

| マイクロアーキテクチャ | 高速化 | タイミング故障検出 |

[背景]ばらつきの増加による平均的な回路遅延とクロック周波数設定の乖離

[問題]ステージ間で実際の遅延を融通するクロッキング方式を回路に適用する方法が未確立だった

[貢献]手法を回路に自動適用する方法を確立した

プロセッサのクロック周波数を制約する要因の1つは回路素子遅延である.プロセッサが正しく動作するためには,フリップ・フロップやラッチといった記憶素子から出発して,何らかの組み合わせ回路を通って,次の記憶素子に至るまでの処理時間が,クロックの一周期分の時間よりも短くなければならない.これを満たさないと,記憶素子は間違った値を記憶してしまう.間違った値が記憶されてしまったとき,タイミング故障が起きているという.

この処理時間はさまざまな要因でばらつく.ばらつくので,最悪の(遅延の最も大きい)場合でも動作するようにクロック周波数は決定される.これをワースト・ケース設計と呼ぶ.しかし,ばらつきが大きいとワースト・ケース設計は悲観的になりすぎる.

この問題に対処するため,動作時にタイミング故障を検出し,回復する手法が提案された.この手法では,ワースト・ケース設計より高いクロックで動作させて,万が一タイミング故障が発生したとしても,回復が可能である.故障から回復するときはペナルティを被るが,故障が起きることが稀ならば,多くの場合において高いクロックで動作するため,総合的には性能を改善することができる.

私の所属した研究室では,タイミング故障検出と二相ラッチ方式という方式を組み合わせることで,性能向上において従来手法を超える,新しいクロッキング方式を提案してきた.この手法はクロック周波数を最大2倍にし,従来手法に比べてタイミング故障が起こる確率が少なくなることが期待される.

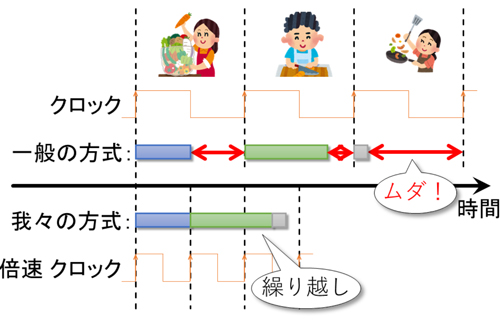

このクロッキング方式はステージ間の遅延の融通を可能にする.そのイメージを下図に示す.図では,料理によりプロセッサの処理を喩えており,色のついた棒によって,料理の各ステージ(野菜をそろえる,切る,炒める)の実際の遅延時間を示している.一般的なクロッキング方式では,赤い矢印で示すような無駄が生じる.一方で,我々の方式では無駄がない.我々の方式では「そろえる」が終わった直後に「切る」を開始でき,さらに「切る」で長い時間がかかっても,遅延を繰り越し,故障が起きない.このように,我々の方式では,実際の遅延をステージ間で融通し,処理をタイミング故障なく終えることができる.

課題として,タイミング故障を検出する手法について,ダイナミック・プリチャージ・ロジック,特に SRAMへの適用が考慮されてこなかった.また,我々の方式は簡単な回路によって最低限の動作確認がされただけであった.実用化のためには,最終的には,Out-of-Orderスーパースカラ・プロセッサなどの現実的な回路に対して適用した上で,LSI化し,評価を行う必要がある.また,既存の回路を入力として,方式が適用された回路を出力する自動変換ツールの開発が不可欠であった.

私の研究では,その最終段階までには至ってはいないが,そのための重要なステップとして,以下を行った:

1.SRAMを対象としたタイミング故障検出手法の適用

2.自動変換手法の確立

3.二相ラッチ化手法の確立

4.タイミング故障検出のスカラ・プロセッサへの適用

[貢献]手法を回路に自動適用する方法を確立した

プロセッサのクロック周波数を制約する要因の1つは回路素子遅延である.プロセッサが正しく動作するためには,フリップ・フロップやラッチといった記憶素子から出発して,何らかの組み合わせ回路を通って,次の記憶素子に至るまでの処理時間が,クロックの一周期分の時間よりも短くなければならない.これを満たさないと,記憶素子は間違った値を記憶してしまう.間違った値が記憶されてしまったとき,タイミング故障が起きているという.

この処理時間はさまざまな要因でばらつく.ばらつくので,最悪の(遅延の最も大きい)場合でも動作するようにクロック周波数は決定される.これをワースト・ケース設計と呼ぶ.しかし,ばらつきが大きいとワースト・ケース設計は悲観的になりすぎる.

この問題に対処するため,動作時にタイミング故障を検出し,回復する手法が提案された.この手法では,ワースト・ケース設計より高いクロックで動作させて,万が一タイミング故障が発生したとしても,回復が可能である.故障から回復するときはペナルティを被るが,故障が起きることが稀ならば,多くの場合において高いクロックで動作するため,総合的には性能を改善することができる.

私の所属した研究室では,タイミング故障検出と二相ラッチ方式という方式を組み合わせることで,性能向上において従来手法を超える,新しいクロッキング方式を提案してきた.この手法はクロック周波数を最大2倍にし,従来手法に比べてタイミング故障が起こる確率が少なくなることが期待される.

このクロッキング方式はステージ間の遅延の融通を可能にする.そのイメージを下図に示す.図では,料理によりプロセッサの処理を喩えており,色のついた棒によって,料理の各ステージ(野菜をそろえる,切る,炒める)の実際の遅延時間を示している.一般的なクロッキング方式では,赤い矢印で示すような無駄が生じる.一方で,我々の方式では無駄がない.我々の方式では「そろえる」が終わった直後に「切る」を開始でき,さらに「切る」で長い時間がかかっても,遅延を繰り越し,故障が起きない.このように,我々の方式では,実際の遅延をステージ間で融通し,処理をタイミング故障なく終えることができる.

課題として,タイミング故障を検出する手法について,ダイナミック・プリチャージ・ロジック,特に SRAMへの適用が考慮されてこなかった.また,我々の方式は簡単な回路によって最低限の動作確認がされただけであった.実用化のためには,最終的には,Out-of-Orderスーパースカラ・プロセッサなどの現実的な回路に対して適用した上で,LSI化し,評価を行う必要がある.また,既存の回路を入力として,方式が適用された回路を出力する自動変換ツールの開発が不可欠であった.

私の研究では,その最終段階までには至ってはいないが,そのための重要なステップとして,以下を行った:

1.SRAMを対象としたタイミング故障検出手法の適用

2.自動変換手法の確立

3.二相ラッチ化手法の確立

4.タイミング故障検出のスカラ・プロセッサへの適用

(2019年6月1日受付)