(邦訳:HDLチェックポインティングを用いた耐故障かつ拡張可能なFPGAコンピューティング)

| Vu Hoang Gia レクイドン工科大学 助教 |

[背景]限られた資源を有効利用するためにFPGAコンピューティングにチェックポインティングが必要

[問題]FPGAの全状態を保存/復元する従来手法ではオーバヘッドが非常に大きい

[貢献]高速かつ最小限の追加回路でチェックポインティングを実現するアーキテクチャの提案

[問題]FPGAの全状態を保存/復元する従来手法ではオーバヘッドが非常に大きい

[貢献]高速かつ最小限の追加回路でチェックポインティングを実現するアーキテクチャの提案

FPGAは再構成可能な高い計算性能と高い電力効率によって,専用用途向け高性能計算基盤として世界の多くのデータセンターで利用されています.具体的には,マイクロソフトのCatapult,Amazon EC2のF1インスタンス,BaidoのSDA,IBMやNovo-Gフォーラムなどで採用が進んでいます.

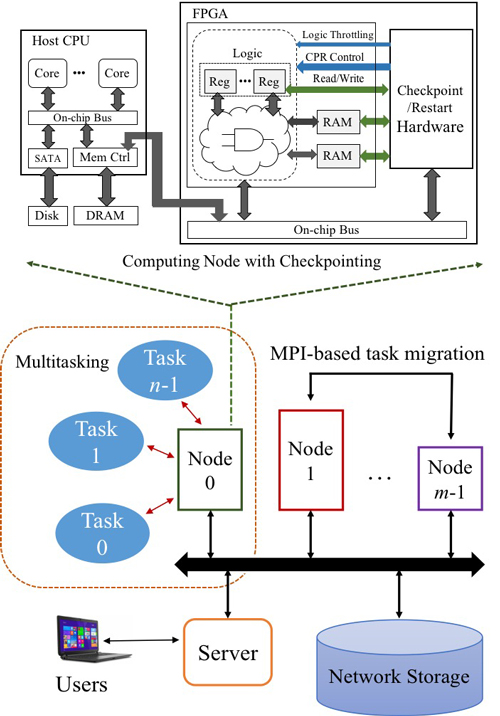

しかし,このようにFPGAが広く採用されるようになると,いくつかの問題が明らかになってきました.最も重要な課題は信頼性の問題です.計算時間が長くなるにつれ実行中のエラーに対する備えが重要になってきます.本研究ではタスクの中断/再開(Checkpointing/Restart)機能によりこの問題を解決しました.

本研究ではCPRflattenと名付けたチェックポインティングアーキテクチャを提案しました.リング型やツリー型のアーキテクチャを検討した結果,リング型をベースとして追加回路の最適化を行うことにより高速かつ回路オーバヘッドの最小化ができることがわかりました.また,この機能の実装を自動化するためのPythonを用いたフレームワークを構築しました.このフレームワークを用いることで,ハードウェアオーバヘッドが自動的に最小化されます.

この提案手法を応用することにより,FPGAコンピューティングの拡張容易性についても大幅に改善できます.チェックポインティングを利用することにより,FPGA上でのタスクの動的切り替えや時分割による多重実行機能が可能になります.また,実行中のアプリケーションの実行ノードを途中で変更できるため,システムの柔軟な運用も可能になります.具体的には,負荷バランスの動的調整やメンテナンスのためのシステムの一部停止をユーザーに気付かれることなく行うことができます.その結果,複数のユーザーで同一のFPGA環境を共有し,必要に応じてFPGA上で実行するプログラムを自動的に切り替えることで,FPGAのマルチタスクを実現しました.さらには,規模も製造元も異なるFPGA間でのプログラムの自動切り替えも実現可能としました.

これらの成果により,より自由かつ効率的なFPGAコンピューティングが実現可能となります.

しかし,このようにFPGAが広く採用されるようになると,いくつかの問題が明らかになってきました.最も重要な課題は信頼性の問題です.計算時間が長くなるにつれ実行中のエラーに対する備えが重要になってきます.本研究ではタスクの中断/再開(Checkpointing/Restart)機能によりこの問題を解決しました.

本研究ではCPRflattenと名付けたチェックポインティングアーキテクチャを提案しました.リング型やツリー型のアーキテクチャを検討した結果,リング型をベースとして追加回路の最適化を行うことにより高速かつ回路オーバヘッドの最小化ができることがわかりました.また,この機能の実装を自動化するためのPythonを用いたフレームワークを構築しました.このフレームワークを用いることで,ハードウェアオーバヘッドが自動的に最小化されます.

この提案手法を応用することにより,FPGAコンピューティングの拡張容易性についても大幅に改善できます.チェックポインティングを利用することにより,FPGA上でのタスクの動的切り替えや時分割による多重実行機能が可能になります.また,実行中のアプリケーションの実行ノードを途中で変更できるため,システムの柔軟な運用も可能になります.具体的には,負荷バランスの動的調整やメンテナンスのためのシステムの一部停止をユーザーに気付かれることなく行うことができます.その結果,複数のユーザーで同一のFPGA環境を共有し,必要に応じてFPGA上で実行するプログラムを自動的に切り替えることで,FPGAのマルチタスクを実現しました.さらには,規模も製造元も異なるFPGA間でのプログラムの自動切り替えも実現可能としました.

これらの成果により,より自由かつ効率的なFPGAコンピューティングが実現可能となります.

(2018年5月22日受付)