(邦訳:高電力効率プロセッサのためのキャッシュの設計最適化)

| 有間 英志 東京大学 情報基盤センター 特任助教 |

[背景]高電力効率なプロセッサの必要性

[問題]キャッシュがプロセッサの電力効率を大きく左右

[貢献]キャッシュの設計を最適化するための方法論の導出

[問題]キャッシュがプロセッサの電力効率を大きく左右

[貢献]キャッシュの設計を最適化するための方法論の導出

近年,高性能計算機システムから組み込みシステムに至るまで,あらゆる計算機システムにおいて電力効率(性能/消費電力)の改善が求められている.特に携帯端末においては,高性能化の要求は高まりつつある一方,バッテリーを長持ちさせるために消費電力を抑える必要があり,その電力効率の大幅な向上は急務である.

計算機システムの構成要素の中でも特にその電力効率を左右するのがプロセッサであり,その中でも特に性能・消費電力への影響が大きいのがキャッシュと呼ばれるデータを一時的に保持しておく領域である.これは,昨今のプロセッサにおいてはキャッシュのヒット率が性能を大きく左右し,さらにはプロセッサチップ内で膨大な面積を占めるキャッシュに対して,データ保持のために電力を供給し続ける必要があり,その消費電力も無視できないためである.

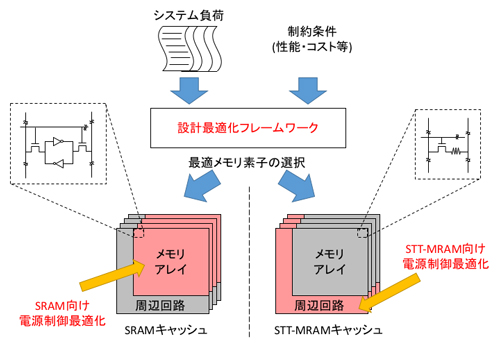

そこで本研究では,携帯端末で用いられる汎用プロセッサに焦点を当て,その電力効率を向上させるためのキャッシュの制御および設計の最適化を行っている.具体的には,既存のSRAM素子だけでなくSTT-MRAMと呼ばれるデータ保持に電力供給の必要のない不揮発性メモリ素子の利用も考慮し,システムに与えられる負荷,システムの性能,コスト制約,各メモリ素子の特性等さまざまな条件を勘案してこれらメモリ素子の中から適切なものを選択し,選択したメモリ素子の性質に応じてその電源制御を最適化するというものである.具体的には以下3点の提案から成る.

まず,SRAMキャッシュ向け電源制御最適化手法を提案している.SRAMキャッシュにおいては,電源遮断を行うことで消費電力を抑えることができるが,その反面データ損失によってキャッシュヒット率が低下し,性能が悪化するという問題があった.そこで本研究では,電源遮断によって損失したデータの内,今後も再び利用しそうなものを予測し,事前にメインメモリからキャッシュに読み込むという手法を提案している.それによって,性能低下を大幅に防ぐことができ,結果として電源遮断機会を増加させることができる.

次に,STT-MRAMキャッシュ向け電源制御手法を提案している.STT-MRAMキャッシュでは,周辺回路と呼ばれるデータアレイへのアクセスを制御する回路の消費電力が問題となっている.この周辺回路に対して電源遮断を適用することで,消費電力を抑えることができるが,電源復帰に長い時間を要するために性能低下を引き起こす.そこで本研究では,データアレイに対する次のアクセスが性能にクリティカルかどうかを予測し,クリティカルでない場合のみ電源遮断を行うという制御手法によってこの問題に対処している.

さらに,上記提案手法を勘案した上で,与えられるシステムの負荷に応じて,性能,コスト制約の下,電力を最小化するようにキャッシュの設計最適化を行うためのフレームワークの導出およびそれを用いた評価を行っている.それによって,さまざまな条件下において利用すべきメモリ素子が明らかとなり,それに対して上記提案電源制御手法を適用することで,プロセッサの電力効率を大幅に向上できる.

計算機システムの構成要素の中でも特にその電力効率を左右するのがプロセッサであり,その中でも特に性能・消費電力への影響が大きいのがキャッシュと呼ばれるデータを一時的に保持しておく領域である.これは,昨今のプロセッサにおいてはキャッシュのヒット率が性能を大きく左右し,さらにはプロセッサチップ内で膨大な面積を占めるキャッシュに対して,データ保持のために電力を供給し続ける必要があり,その消費電力も無視できないためである.

そこで本研究では,携帯端末で用いられる汎用プロセッサに焦点を当て,その電力効率を向上させるためのキャッシュの制御および設計の最適化を行っている.具体的には,既存のSRAM素子だけでなくSTT-MRAMと呼ばれるデータ保持に電力供給の必要のない不揮発性メモリ素子の利用も考慮し,システムに与えられる負荷,システムの性能,コスト制約,各メモリ素子の特性等さまざまな条件を勘案してこれらメモリ素子の中から適切なものを選択し,選択したメモリ素子の性質に応じてその電源制御を最適化するというものである.具体的には以下3点の提案から成る.

まず,SRAMキャッシュ向け電源制御最適化手法を提案している.SRAMキャッシュにおいては,電源遮断を行うことで消費電力を抑えることができるが,その反面データ損失によってキャッシュヒット率が低下し,性能が悪化するという問題があった.そこで本研究では,電源遮断によって損失したデータの内,今後も再び利用しそうなものを予測し,事前にメインメモリからキャッシュに読み込むという手法を提案している.それによって,性能低下を大幅に防ぐことができ,結果として電源遮断機会を増加させることができる.

次に,STT-MRAMキャッシュ向け電源制御手法を提案している.STT-MRAMキャッシュでは,周辺回路と呼ばれるデータアレイへのアクセスを制御する回路の消費電力が問題となっている.この周辺回路に対して電源遮断を適用することで,消費電力を抑えることができるが,電源復帰に長い時間を要するために性能低下を引き起こす.そこで本研究では,データアレイに対する次のアクセスが性能にクリティカルかどうかを予測し,クリティカルでない場合のみ電源遮断を行うという制御手法によってこの問題に対処している.

さらに,上記提案手法を勘案した上で,与えられるシステムの負荷に応じて,性能,コスト制約の下,電力を最小化するようにキャッシュの設計最適化を行うためのフレームワークの導出およびそれを用いた評価を行っている.それによって,さまざまな条件下において利用すべきメモリ素子が明らかとなり,それに対して上記提案電源制御手法を適用することで,プロセッサの電力効率を大幅に向上できる.

(2016年6月6日受付)