(邦訳:ビアスイッチクロスバーを用いたFPGAにおけるスニークパス問題回避と故障診断)

| 土井 龍太郎 (正会員) NEC中央研究所 研究員 |

キーワード

| 不揮発ビアスイッチFPGA | クロスバープログラミング | 故障テスト |

[背景]高エネルギー効率なビアスイッチFPGAの実用化への期待

[問題]再構成時のスニークパス問題,未確立の故障テスト手法

[貢献]スイッチ書き換え順の最適化によるスニークパス問題根本解消,故障素子を特定する故障診断手法

集積回路チップを構成するトランジスタは半世紀以上にわたって微細化を続けており,今では髪の毛の1万分の1程度の非常に小さい世界でトランジスタは作られています.微細化は回路の処理速度の向上や消費電力の削減などのメリットがある反面,チップの開発費が高額になってしまうデメリットもあります.たとえば,最先端のトランジスタを使ってゼロからチップを作る場合,何百億円という費用がかかります.そこで,ゼロからチップを作るのではなく,FPGA(field programmable gate array)と呼ばれる製造後に回路機能を自由にプログラムできる再構成可能チップを利用して,行いたい処理を実装するというアプローチがしばしば採用されます.

しかし,既存のFPGAには面積の大きいSRAM(static random access memory)スイッチが大量に搭載されるため,エネルギー効率が低いという欠点が存在します.その欠点を解消するため,SRAMスイッチをビアスイッチと呼ばれる小面積な新ナノデバイスで置き換えた高エネルギー効率な次世代FPGAの研究が行われています.私の研究では,そのビアスイッチFPGAの実用化における以下の2つの課題に取り組みました.

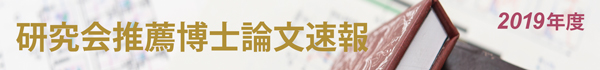

(1)スイッチ書き換え順の最適化によるスニークパス問題根本解消

ビアスイッチFPGA内部では,格子状に存在する縦横の配線の各交点にビアスイッチを配置したクロスバーと呼ばれる回路を活用します.これらのビアスイッチのオン・オフ状態を書き換えて,配線同士の接続・非接続を切り替えることで回路機能がプログラムできます.しかし,ビアスイッチのオン・オフ状態のパターンによっては,スイッチの書き換え時に別のスイッチが意図せず書き換わってしまうスニークパス問題が発生してしまいます.スニークパス問題が起きてしまうとFPGAを正しくプログラムできなくなるため,大きな問題でした.

私の研究ではスイッチを書き換える順番を調整することでスニークパス問題を回避できる新事実を発見し,配線の接続状況をグラフの一種である木構造を用いて表現することで,最適なスイッチ書き換え順を効率良く導き出す手法を考案しました.そして,この手法を用いると実用上すべてのオン・オフ状態パターンにおいてスニークパス問題が発生しないことを証明しました.

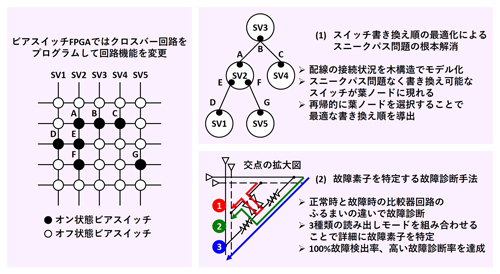

(2)故障素子を特定する故障診断手法

ビアスイッチFPGAを製造した後には,不良品をユーザに出荷することを防ぐために,故障の有無を検査する必要があります.しかし,ビアスイッチFPGAをどのように検査すればよいかは明らかではありませんでした.

私の研究では,比較器と呼ばれる回路を使うことでクロスバー上のビアスイッチの故障状態が読み出せることをシミュレーションで確認しました.そして,3種類の読み出しモードを組み合わせることで詳細に故障テストできる手法を提案しました.提案手法によって,ビアスイッチが故障しているかどうかは100%判定でき,さらにビアスイッチを構成する4つの素子のうち,どの素子がどのように故障しているかについても高精度に突き止めることが可能になりました.詳細な故障テストは良品・不良品の検査以外にも,歩留まり解析などにも有用です.

[貢献]スイッチ書き換え順の最適化によるスニークパス問題根本解消,故障素子を特定する故障診断手法

集積回路チップを構成するトランジスタは半世紀以上にわたって微細化を続けており,今では髪の毛の1万分の1程度の非常に小さい世界でトランジスタは作られています.微細化は回路の処理速度の向上や消費電力の削減などのメリットがある反面,チップの開発費が高額になってしまうデメリットもあります.たとえば,最先端のトランジスタを使ってゼロからチップを作る場合,何百億円という費用がかかります.そこで,ゼロからチップを作るのではなく,FPGA(field programmable gate array)と呼ばれる製造後に回路機能を自由にプログラムできる再構成可能チップを利用して,行いたい処理を実装するというアプローチがしばしば採用されます.

しかし,既存のFPGAには面積の大きいSRAM(static random access memory)スイッチが大量に搭載されるため,エネルギー効率が低いという欠点が存在します.その欠点を解消するため,SRAMスイッチをビアスイッチと呼ばれる小面積な新ナノデバイスで置き換えた高エネルギー効率な次世代FPGAの研究が行われています.私の研究では,そのビアスイッチFPGAの実用化における以下の2つの課題に取り組みました.

(1)スイッチ書き換え順の最適化によるスニークパス問題根本解消

ビアスイッチFPGA内部では,格子状に存在する縦横の配線の各交点にビアスイッチを配置したクロスバーと呼ばれる回路を活用します.これらのビアスイッチのオン・オフ状態を書き換えて,配線同士の接続・非接続を切り替えることで回路機能がプログラムできます.しかし,ビアスイッチのオン・オフ状態のパターンによっては,スイッチの書き換え時に別のスイッチが意図せず書き換わってしまうスニークパス問題が発生してしまいます.スニークパス問題が起きてしまうとFPGAを正しくプログラムできなくなるため,大きな問題でした.

私の研究ではスイッチを書き換える順番を調整することでスニークパス問題を回避できる新事実を発見し,配線の接続状況をグラフの一種である木構造を用いて表現することで,最適なスイッチ書き換え順を効率良く導き出す手法を考案しました.そして,この手法を用いると実用上すべてのオン・オフ状態パターンにおいてスニークパス問題が発生しないことを証明しました.

(2)故障素子を特定する故障診断手法

ビアスイッチFPGAを製造した後には,不良品をユーザに出荷することを防ぐために,故障の有無を検査する必要があります.しかし,ビアスイッチFPGAをどのように検査すればよいかは明らかではありませんでした.

私の研究では,比較器と呼ばれる回路を使うことでクロスバー上のビアスイッチの故障状態が読み出せることをシミュレーションで確認しました.そして,3種類の読み出しモードを組み合わせることで詳細に故障テストできる手法を提案しました.提案手法によって,ビアスイッチが故障しているかどうかは100%判定でき,さらにビアスイッチを構成する4つの素子のうち,どの素子がどのように故障しているかについても高精度に突き止めることが可能になりました.詳細な故障テストは良品・不良品の検査以外にも,歩留まり解析などにも有用です.

(2020年5月31日受付)