| 西澤 真一 埼玉大学大学院理工学研究科 助教 |

[背景]集積回路製造プロセスの微細化によるエネルギー効率向上の限界

[問題]微細プロセスにおけるエネルギー効率の高い集積回路設計技術が必要

[貢献]性能ばらつき予測技術および低電圧回路向けセルライブラリによる低消費エネルギー集積回路設計環境の構築

[問題]微細プロセスにおけるエネルギー効率の高い集積回路設計技術が必要

[貢献]性能ばらつき予測技術および低電圧回路向けセルライブラリによる低消費エネルギー集積回路設計環境の構築

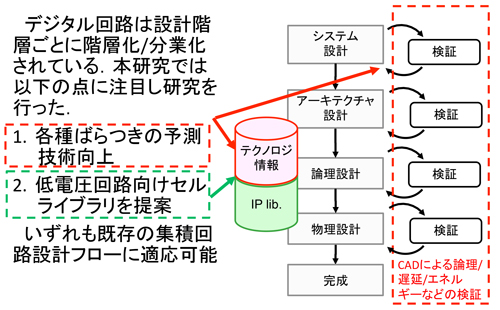

集積回路はこれまでその製造プロセスの微細化によって処理速度の高速化,多機能化,低消費エネルギー化を実現してきた.しかし加工寸法が100nmを切るような微細プロセスでは,微細なトランジスタや配線素子の製造上および設計上の問題が顕在化してきている.ひとつは素子特性のばらつきが回路特性に与える影響が拡大していることである.製造プロセスの複雑化によって,トランジスタ特性ばらつきが複雑化している.そのためばらつきの正確なモデル化と設計への反映が必要である.もうひとつは,微細プロセスにおいて微細化による消費エネルギー削減効果が減少していることである.リーク電流の影響によって,トランジスタの閾値電圧を下げることができないためである.電源電圧の低下は回路のエネルギー効率を改善することが可能であるが,電源電圧の低下によって回路遅延が大きくなり,また各種ばらつきが回路特性に与える影響が拡大する.そのためエネルギー効率の高い集積回路を実現するためには,低電圧回路に適した構造を持つ回路を設計する必要がある.

本研究では,集積回路のエネルギー効率の向上を目的として,大きく以下の2つの問題について取り組んだ.

(1)性能ばらつきの予測技術の向上によるエネルギー効率の向上

集積回路における素子特性ばらつきを考慮するために設計時にマージンを設けているが,不適切な設計マージンの設定は無駄な消費エネルギーの増加や,性能歩留まりの悪化につながる.性能ばらつきを適切に予測するために,製造プロセスに起因する回路遅延ばらつきの統計的性質に応じた分離手法の高精度化,電源配線構造に起因する電圧ばらつきを評価するための埋め込みモニタ回路の検討を行った.実際の集積回路における回路遅延ばらつき統計的性質の分離,および電源電圧ばらつきモニタ回路の観測結果から,提案手法の妥当性を検証した.

(2)エネルギー効率の高い低電圧ディジタル回路を実現するスタンダードセルライブラリの構築

電源電圧を下げることは集積回路のエネルギー効率を改善する有効な手法であるが,電源電圧を下げると回路遅延は増大し,また製造プロセスに起因するトランジスタ特性ばらつきが拡大する.そのため,低電圧動作に適したスタンダードセルの構成法について検討をした.トランジスタの電圧電流特性は電源電圧とトランジスタの直列数に依存することから,回路の動作電圧に合わせてスタンダードセルごとにトランジスタのゲート幅の最適化が容易なレイアウト構造を提案した.また,低電圧動作において拡大する製造プロセスに起因するトランジスタ特性ばらつきを考慮した順序セルの設計法について検討を行った.モンテカルロシミュレーションを利用した加速試験を行い,製造プロセスばらつきに脆弱なトランジスタを見つけ出すことで,順序セルの設計改善を可能にした.

本研究では,集積回路のエネルギー効率の向上を目的として,大きく以下の2つの問題について取り組んだ.

(1)性能ばらつきの予測技術の向上によるエネルギー効率の向上

集積回路における素子特性ばらつきを考慮するために設計時にマージンを設けているが,不適切な設計マージンの設定は無駄な消費エネルギーの増加や,性能歩留まりの悪化につながる.性能ばらつきを適切に予測するために,製造プロセスに起因する回路遅延ばらつきの統計的性質に応じた分離手法の高精度化,電源配線構造に起因する電圧ばらつきを評価するための埋め込みモニタ回路の検討を行った.実際の集積回路における回路遅延ばらつき統計的性質の分離,および電源電圧ばらつきモニタ回路の観測結果から,提案手法の妥当性を検証した.

(2)エネルギー効率の高い低電圧ディジタル回路を実現するスタンダードセルライブラリの構築

電源電圧を下げることは集積回路のエネルギー効率を改善する有効な手法であるが,電源電圧を下げると回路遅延は増大し,また製造プロセスに起因するトランジスタ特性ばらつきが拡大する.そのため,低電圧動作に適したスタンダードセルの構成法について検討をした.トランジスタの電圧電流特性は電源電圧とトランジスタの直列数に依存することから,回路の動作電圧に合わせてスタンダードセルごとにトランジスタのゲート幅の最適化が容易なレイアウト構造を提案した.また,低電圧動作において拡大する製造プロセスに起因するトランジスタ特性ばらつきを考慮した順序セルの設計法について検討を行った.モンテカルロシミュレーションを利用した加速試験を行い,製造プロセスばらつきに脆弱なトランジスタを見つけ出すことで,順序セルの設計改善を可能にした.

(2014年6月10日受付)